智能体AI时代:CPU角色定位的第一性原理分析战略洞察者

第一章:负载本质拆解 Agentic AI对计算资源的重新排序

1. 从“黑盒推理”到“系统编排”

2. CPU关键能力的第一性排序

3. 延迟占比实证:消失的GPU主导权

第二章:计算架构实证 从GB300到Vera Rubin的解耦真相

1. 机架内比例的稳定性:营销幻觉与硬件现实

2. “资源解耦”的真实意图:独立Vera CPU机架的崛起

3. 数据中心作为计算单元:跨机架调度的“神经系统”

第三章:部署范式分析——Hyperscalers的ARM自研化之路

1. 功率比的结构性位移:从配角到独立建筑

2. ARM自研CPU的吞噬效应:新增需求的内部消化

3. 对x86市场的真实挤压:并存逻辑下的生存空间

第四章:供应链与制造现实——先进制程的垄断与风险

1. TSMC的绝对主导:被GPU挤压的CPU生存空间

2. Intel 18A的生死博弈:Clearwater Forest与Diamond Rapids重塑之路

3. AMD Venice的市场机会:SMT在并发场景下的溢价空间

第五章:核心逻辑模型——协同演进与吞吐极值

1. 协同演进模型构建:决定成败的“木桶短板”

2. 瓶颈位移预测:计算正在变得“廉价”,而编排依然“昂贵”

3. 战略地位重定义:从“指令分发者”到“全系统状态管理者”

实证对比表:Agentic AI下的厂商架构策略

核心策略深度拆解:从“算力博弈”到“编排主权”

[正文内容]

智能体AI时代:CPU角色定位的第一性原理分析

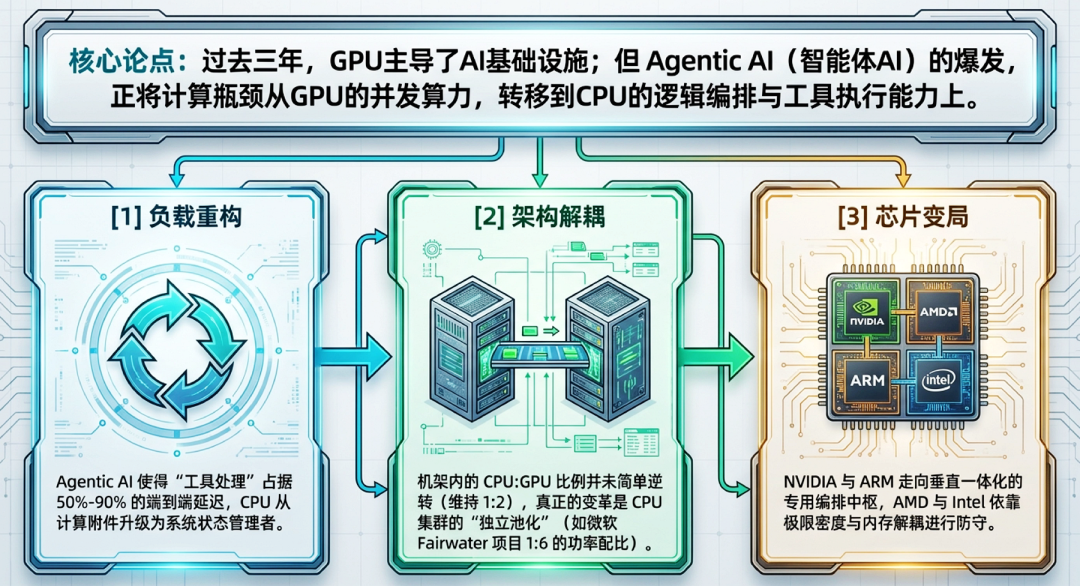

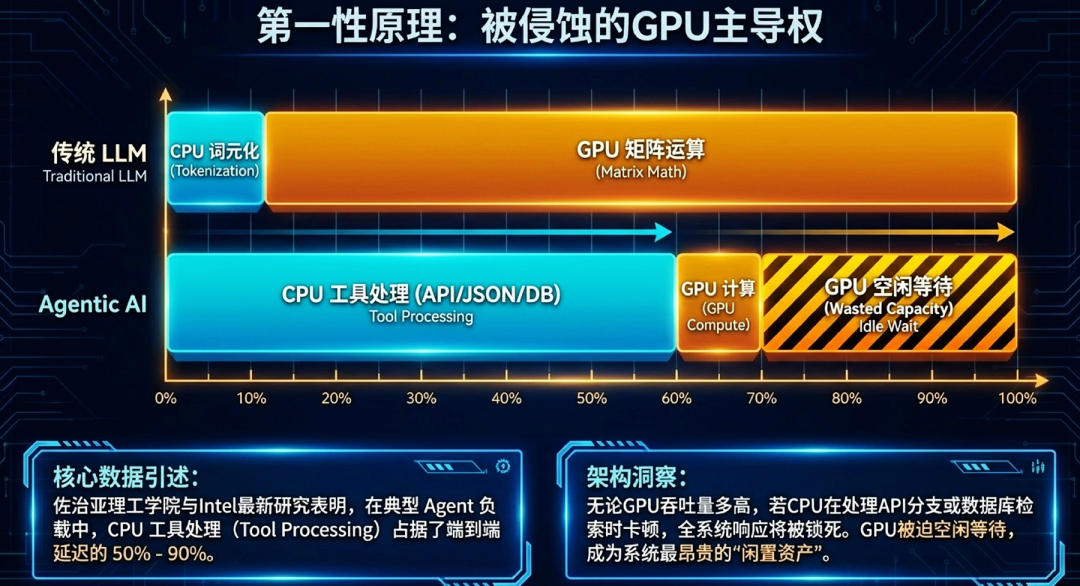

Agentic AI(智能体AI)的兴起正驱动数据中心架构发生第一性原理级别的重构。不同于传统AI的单一矩阵运算,智能体AI工作负载以“感知-规划-执行-反馈”的长序列闭环为特征,将计算瓶颈从GPU算力引向CPU的编排与工具执行能力。实证表明,CPU已从单纯的“头节点”演进为与GPU解耦的独立关键资源池。尽管NVIDIA等厂商在架内维持GPU中心化设计,但超大规模云服务商通过建设独立CPU集群(如Microsoft Fairwater项目)来应对结构性增量。未来系统吞吐量将受限于“GPU推理”与“CPU编排”的协同极值。

第一章:负载本质拆解 Agentic AI对计算资源的重新排序

在过去三年的AI基础设施建设中,行业普遍遵循“GPU中心化”的逻辑。在这种范式下,CPU被简化为单纯的“头节点”(Head Node),主要任务是词元化输入、启动GPU内核并处理最终的输出逻辑。然而,随着智能体(Agent)的兴起,这种简单的线性负载结构正被一种复杂的循环逻辑所取代。

1.从“黑盒推理”到“系统编排”

传统的聊天机器人工作流(如ChatGPT)本质上是一种“点对点”的计算:用户输入、GPU矩阵运算、输出响应。而以OpenClaw为代表的持久运行、多智能体(Agent)平台,核心是一个“感知-规划-执行-反馈”的闭环。

在这种新负载下,AI不再仅仅是一个“计算器”,而更像是一个“管理者”。智能体(Agent)需要自主规划任务、调用外部工具(如浏览器、Python解释器、Shell命令)、查询数据库并根据反馈持续迭代。这种转变带来了三个显著特征:

高度的分支依赖:每一轮循环的执行路径完全取决于前一步的工具返回结果,这种高度非确定性、串行的逻辑控制正是GPU的天然弱项。

状态常驻特征:不同于无状态的传统推理,智能体(Agent)需要维护持久的上下文状态(如OpenClaw中的“灵魂”配置文件Soul.md)和长期记忆,这导致计算过程中存在大量的状态读写。

大规模并发:一个复杂的任务可能触发数十甚至数百个子智能体(Agent)并行工作。例如,在自动编写代码时,可能同时有智能体(Agent)在查阅文档、有智能体(Agent)在执行单元测试、有智能体(Agent)在进行跨文件检索。

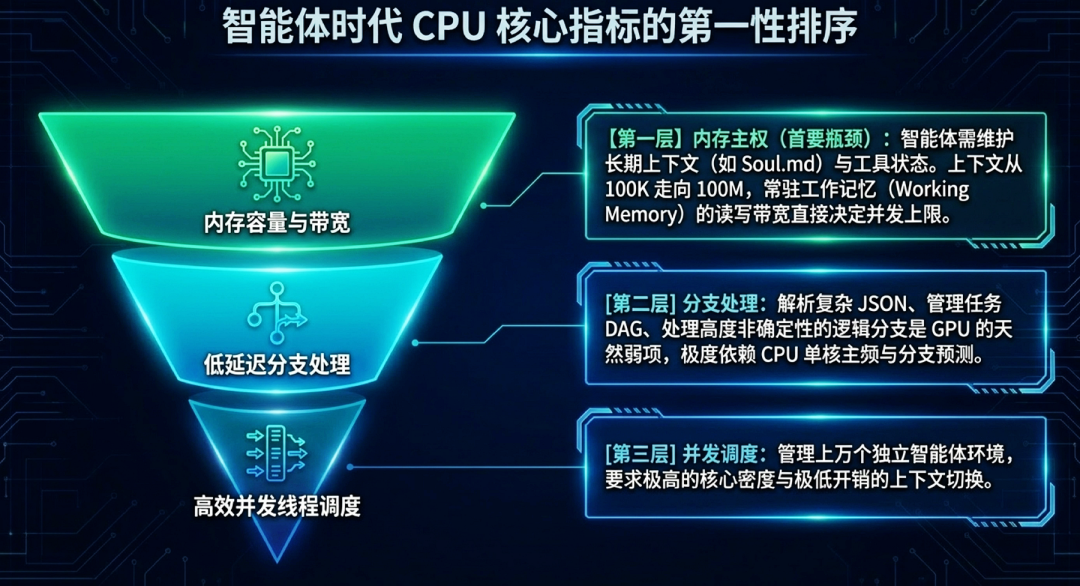

2.CPU关键能力的第一性排序

基于智能体(Agent)的负载本质,我们必须重新定义CPU在计算集群中的角色。从第一性原理出发,CPU的能力需求优先级已经发生了结构性移位:

第一优先级:内存容量与带宽(核心瓶颈)。在智能体(Agent)流程中,上下文(KV Cache)和工具执行状态不再随推理结束而释放,而是作为“工作记忆”常驻。随着上下文窗口从100K冲向100M,存储和检索这些海量状态数据的带宽直接决定了系统的并发支撑上限。例如,AWS Graviton5等新一代CPU大幅增加核心带宽和缓存,正是为了解决状态常驻带来的I/O压力。

第二优先级:低延迟分支处理。智能体(Agent)的大部分工作在于“执行”而非单纯的“思考”。解析复杂的JSON响应、管理任务的有向无环图(DAG)、处理API层的逻辑分支,这些确定性逻辑高度依赖CPU的单核主频和分支预测效率,而非GPU的吞吐算力。

第三优先级:高效线程管理与并发调度。面对数以万计的智能体(Agent)运行环境,CPU必须能在极低开销下管理复杂的上下文切换和并发线程。这要求处理器具备极高的多核心密度(如AmpereOne的192核或Intel Clearwater Forest的288核)以及成熟的并行控制机制。