CPO量产瓶颈:不是制造,是测试华尔街日报

CPO芯片测试涉及电学、光学、光电交互三重复杂性,目前缺乏行业统一标准,大量依赖人工操作。单颗PIC芯片100%检测平均耗时超100秒,光波导与光纤截面积相差近800倍带来的纳米级对准难题,使CPO测试远比传统芯片测试复杂。

当AI数据中心的算力扩张推动CPO走向量产,一个被忽视的环节正成为整条产业链的瓶颈所在——测试。

随着AI数据中心规模持续扩张,传统铜互连已逼近物理极限,共封装光学(CPO)被业界视为下一代AI基础设施的关键互连方案之一。台积电的COUPE平台预计2026年进入量产,CPO正从实验室走向商业化。

然而,CPO的检测与测试环节仍是一道难以逾越的门槛。行业目前缺乏统一标准,流程高度依赖人工,这使得测试成为制约CPO芯片大规模量产的主要瓶颈之一。TrendForce近日发布的研究对这一问题进行了系统梳理。

为什么CPO测试这么难?

理解这个问题,先要理解CPO的结构。

CPO将光学组件集成进光子集成电路(PIC),再与电子集成电路(EIC)共封装在一颗芯片内,用光路替代电路,从而降低功耗和延迟。PIC与EIC键合后的组件称为光学引擎(OE)。

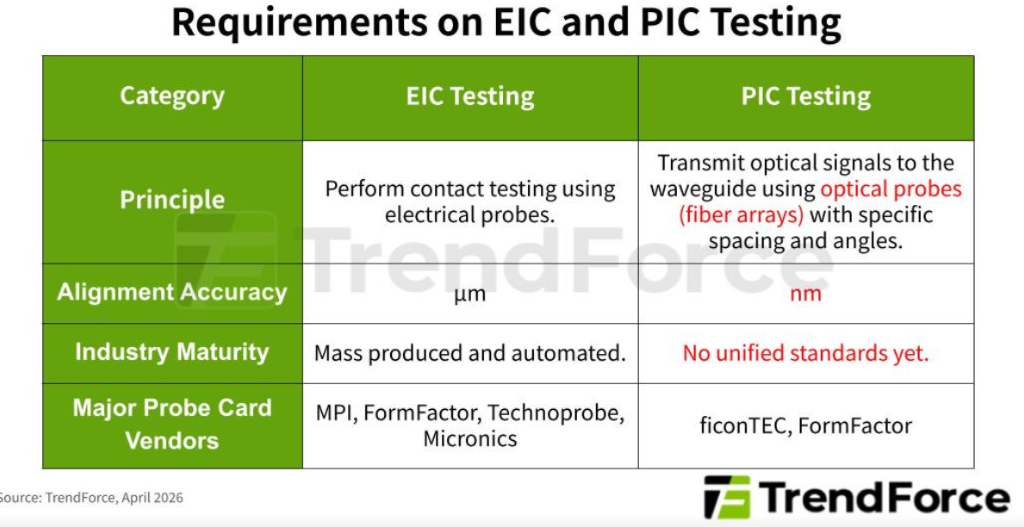

传统EIC测试是纯电学测试,而PIC内部包含耦合器、调制器、光电探测器、光学滤波器、光波导等大量光学组件。测试一个OE,需要同时具备电学、光学和光电交互三方面的专业能力,复杂度远超传统芯片测试。

PIC测试需要测量插入损耗(IL)、偏振相关损耗(PDL)、响应度、波导传播损耗、光学串扰等参数,而这些参数目前没有统一的测试标准。

还有一个更具体的物理难题:光学探针的精准对准。

将外部光从光纤导入OE光波导的过程叫做光耦合。单模光纤纤芯截面积约为78.5平方微米,而光波导截面积仅约0.099平方微米——两者相差近800倍。没有纳米级的对准精度,耦合损耗将极为巨大。

这意味着,光纤阵列必须在距晶圆或芯片表面保持精确间距的同时,对耦合器角度进行微调,以最大化光功率传输,再依次扫描不同波长范围。这套操作目前仍依赖人工完成。

结果是:单颗PIC芯片的100%检测,平均耗时超过100秒。这是CPO芯片量产的核心卡点之一。

“EIC测试与PIC测试对比表”——对比测试原理、对准精度、行业成熟度、主要探针卡厂商四个维度,图源:TrendForce,下同

四个测试阶段,最关键的是哪一步?

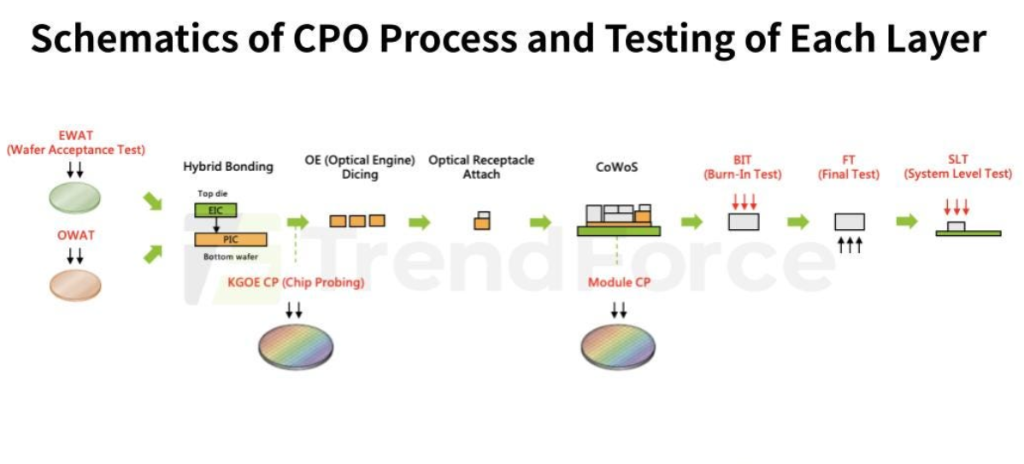

一颗CPO芯片从晶圆到系统,需要经历四个测试阶段:

第一阶段:PIC晶圆级测试(OWAT)——直流电学与光学基础测试,包括光功率、损耗、暗电流等基本光学参数测量。

第二阶段:EIC-PIC晶圆级测试——调制功能测试(电光、光电、光光),高速测试及S参数测量。

第三阶段:OE级测试——全流程校准、直流测试、高速测试、光学回路测试及S参数测量。这是确认"已知良好光学引擎"(KGOE)的关键阶段。

第四阶段:先进封装模块级测试——全系统功能验证与光学回路测试。

四个阶段中,第一阶段PIC晶圆级测试最为关键。

逻辑很直接:PIC通常采用成熟制程制造,而EIC则使用先进制程,成本高昂。如果能在PIC与EIC键合之前,就在晶圆阶段筛出缺陷品,就能避免将昂贵的EIC浪费在有问题的PIC上,大幅降低后续工序的损耗。

这就像流水线上的质检——越早发现问题,损失越小。

"CPO制造流程与测试阶段示意图"——从晶圆验收测试到系统级测试的完整流程图

设备商格局:巨头补课,新玩家入场

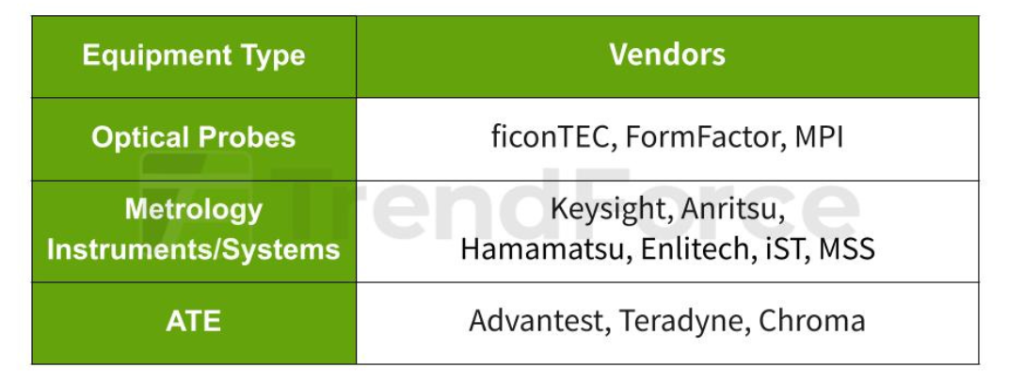

CPO测试设备市场正在加速成形,传统ATE(自动测试设备)巨头与光学测试专业厂商之间的整合是主线。

Advantest与FormFactor

传统EIC测试市场由日本Advantest和美国Teradyne主导。CPO测试要求同时具备EIC和PIC测试能力,两家巨头均选择与光学探针专业厂商合作来补齐短板。

Advantest的路径是与FormFactor合作。2024年6月,Advantest联合Jenoptik和Ayar Labs推出UFO探针卡,将电学和光学探针集成在同一张卡上,实现电光同步测试。其核心创新是对准容差补偿技术——通过对光学探针输出光束进行特殊整形,即使探针定位存在轻微误差,光信号仍能进入PIC耦合器,大幅缩短对准时间。

2025年4月,Advantest与FormFactor进一步推出V93000-Triton光子测试系统,配备9轴光子对准功能和FormFactor的OptoVue Pro光学对准系统。其CalVue技术通过独特设计的逆向反射镜观测光纤阵列,结合自动机器视觉算法实时校准Z轴位移和光学定位,进一步压缩光纤对准时间。

Teradyne与ficonTEC

Teradyne则通过收购和合作双管齐下。2025年,Teradyne收购了Quantifi Photonics,并与德国ficonTEC(现为中国Robo Technik旗下子公司)合作。

2025年3月,双方联合推出业界首款高产量300毫米双面晶圆探针测试系统。ficonTEC提供WLT-D2双面晶圆测试平台,具备50纳米范围的精密对准能力,可同时在晶圆顶面进行电学测试、底面进行光学测试,提升测试效率。Teradyne则提供UltraFLEXplus ATE和IG-XL系统软件。

后续推出的DLT-D1是双面芯片级测试系统,最多可同时连接三个并行测试头,提升吞吐量、降低测试成本。至此,ficonTEC形成了从晶圆级到芯片级的完整CPO测试产品线。

Keysight

Keysight是测量仪器领域的全球领导者,同样提供完整的PIC晶圆测试方案,并与FormFactor集成,兼容FormFactor的Velox探针控制软件。

Keysight的N778x系列偏振合成器可在不同偏振态(SOP)之间快速切换,配合N7700100C偏振Lambda扫描软件,通过矩阵方法推导IL、PDL、TE/TM IL等参数。这套方案无需偏振保持光纤,也无需在多个波长点手动预校正偏振,大幅提升测试效率。其SOP稳定技术还能将输入光的偏振态锁定在特定点,确保整个波长扫描过程中光耦合的稳定性。

Chroma

Chroma是系统级测试(SLT)设备的全球领导者。其光电二极管老化与可靠性测试系统Model 58604/58604-C/58606系列,专为3D传感器件、激光器、光电探测器、调制器等PIC组件的可靠性测试而设计。Model 58606每模块层提供256个SMU通道,最多可配置7层,合计1792个通道。Chroma已宣布将利用其在SLT阶段的光学测试专长,投入CPO测试设备的研发。

Enlitech

2025年9月,Enlitech与iST合作推出Night Jar硅光芯片测试平台。这是一套附加式高光谱成像分析系统,可直接安装在任意品牌探针台上,适用于WAT、CP、FT等各测试阶段。

Night Jar解决的是一个长期存在的行业痛点:此前,光波导中的漏光位置只能通过反射光粗略估计,只能获得总体或平均光损耗值。Night Jar能够精确定位漏光位置,并测量特定波导段或光学组件的量化IL值,支持晶圆级光损耗映射,帮助研发人员更快速准确地识别缺陷,最终提升生产良率。

"CPO测试设备供应链全景表"——涵盖光学探针、计量仪器与系统、自动测试设备三大类别的供应商分布图

市场机会窗口正在打开

芯片设计日趋复杂,SoC测试难度持续上升,单颗芯片所需的测试站数量和总测试时间不断增加,测试设备在半导体设备资本开支中的占比随之提升。随着CPO芯片被纳入产品组合,这一占比预计将进一步走高。

CPO测试设备市场正在成形。从设备商格局来看,传统自动测试设备巨头Advantest和Teradyne正通过并购与合作快速补齐光学能力,Keysight、Chroma、Enlitech等则在各自细分领域占据位置。整个供应链从光学探针、计量仪器到自动测试设备,正在围绕CPO测试需求重新组织。