清华电子AI加速芯片设计:最佳论文水木TsinghuaCent

近日,清华大学电子工程系杨华中教授团队李学清副教授指导的2023级硕士生于天熠在第二十九届欧洲设计、自动化与测试会议(DATE 2026)中荣获最佳论文奖(Best Paper Award)。该论文从大会接收的323篇论文中脱颖而出,被列为12篇最佳论文候选之一,并最终由评审委员会评定为最佳论文。

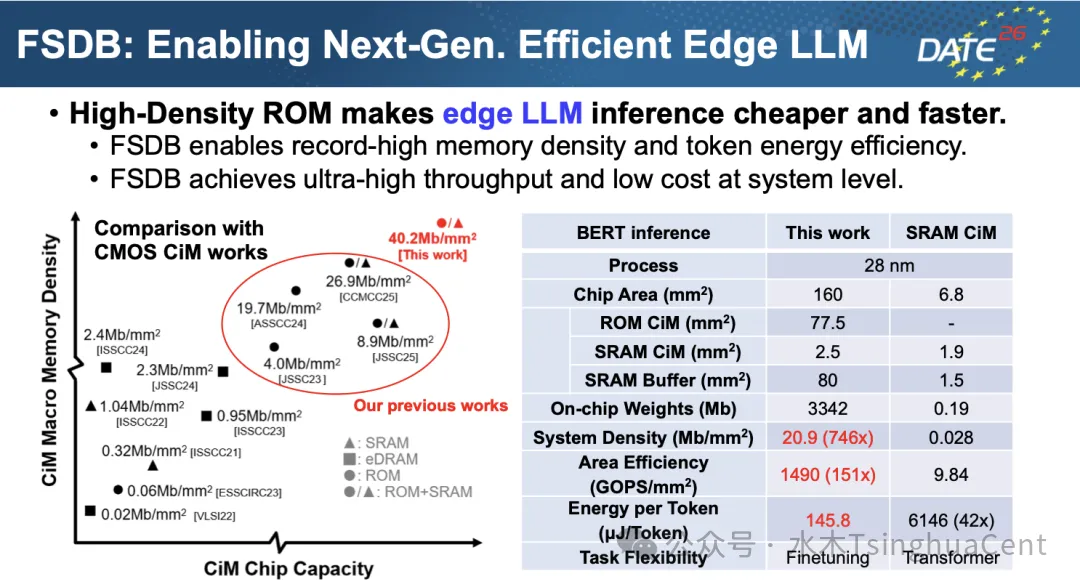

该论文针对传统SRAM存内计算密度低、功耗高,而ROM存内计算权重固定、难以适配不同模型的核心难题,提出了折叠存储与动态扩展的数字混合ROM-SRAM存内计算方案,通过稀疏感知量化与LUT压缩ROM设计,在28nm工艺下实现了40.2 Mb/mm²的全球最高存储密度,大幅提升片上权重承载能力。论文提出的架构创新地实现了ROM卷积核级动态重构,配合SRAM实时重配置,让固定存储的权重具备跨模型的迁移能力,在ImageNet数据集上较现有灵活ROM架构推理精度提升超5%。该研究工作采用可重构流水线计算流程,兼顾W4A8与W8A8运算模式,关键路径延迟降低40%,通过全片上部署权重使片外访存数据量减少90%以上,在多种模型上实现3.3至11.2倍能效提升,同时展现出优异的工艺扩展性,在16nm FinFET节点下存储密度可达94.4 Mb/mm²。 论文的第一作者为课题组的于天熠同学。

欧洲设计、自动化与测试会议(DATE)是电子设计自动化(EDA)与芯片系统领域的顶级国际学术会议之一,与DAC、ICCAD并列全球EDA领域三大旗舰会议,聚焦从集成电路(IC)到片上系统(SoC)、嵌入式系统及测试验证的全链条前沿创新。会议汇聚全球芯片设计、EDA工具、嵌入式系统与硬件测试领域的顶尖学者、工程师及企业代表,覆盖芯片架构创新、EDA设计方法与工具、系统级验证、低功耗与安全设计、AI驱动的芯片设计、测试与可靠性工程等核心方向。最佳论文奖由委员会根据研究的学术创新性、技术实用性以及现场展示效果进行综合评审,最终选拔产生。

李学清副教授长期研究高密度存内计算芯片和高能效神经网络加速架构设计,致力于解决大模型在端侧推理芯片中的功耗与速度瓶颈,特别基于只读存储器(ROM)开展了一系列探索研究。在密度提升方面,团队提出了多比特存储与查找表压缩,在JSSC、TCAS-I、CICC、A-SSCC等国际会议与期刊发表多项代表成果;在灵活性方面,团队提出了ROM-RAM混合架构,使极高密度加速芯片还拥有任务迁移能力,相关成果发表于DAC、ICCAD、DATE等会议。